Overview

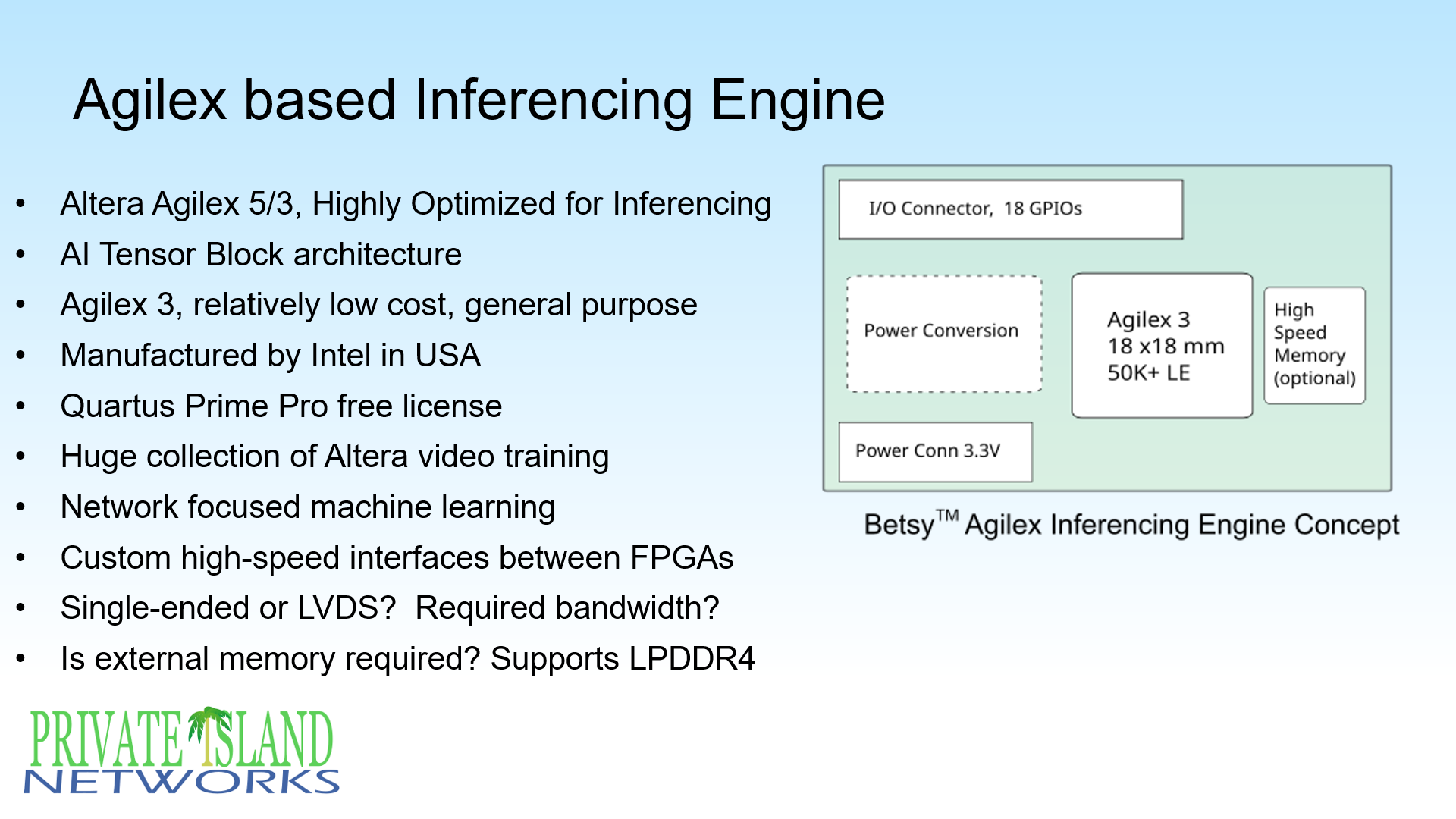

This page summarizes the concept, work items, and status for an FPGA-based machine learning / inferencing module utilizing an Altera Agilex 3 device. The system would initially be realized as a daughter board for the Betsy™ maker board.

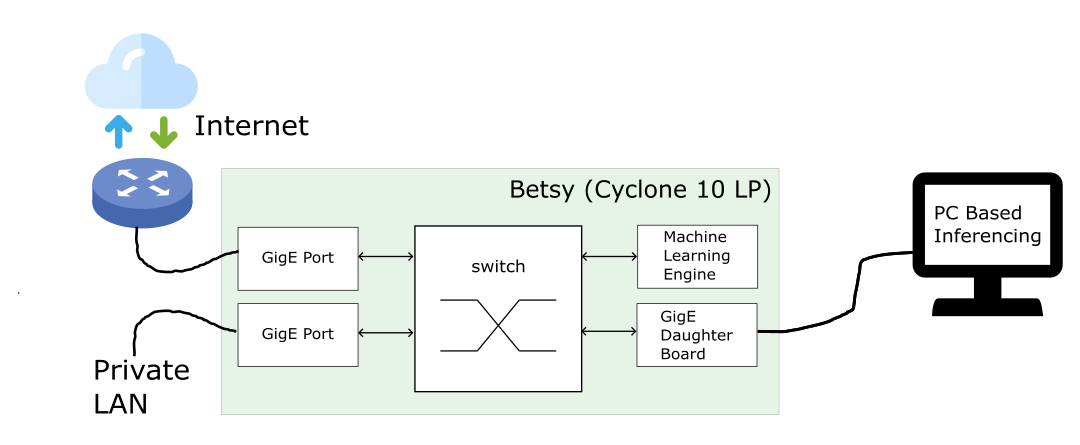

Figure 1 below depicts the existing machine learning architecture with Betsy, a GigE daughter board, and an external PC performing real-time inferencing for network and other applications. Although the Betsy Cyclone 10 LP is well suited for general network processing, data collection, and vector / tensor generation, it lacks a suitable DSP architecture for real-time inferencing except for simple cases.

Note that the Machine Learning Engine block shown below is responsible for pre-processing of network data and generation of vectors / tensors to transfer to an inferencing engine.

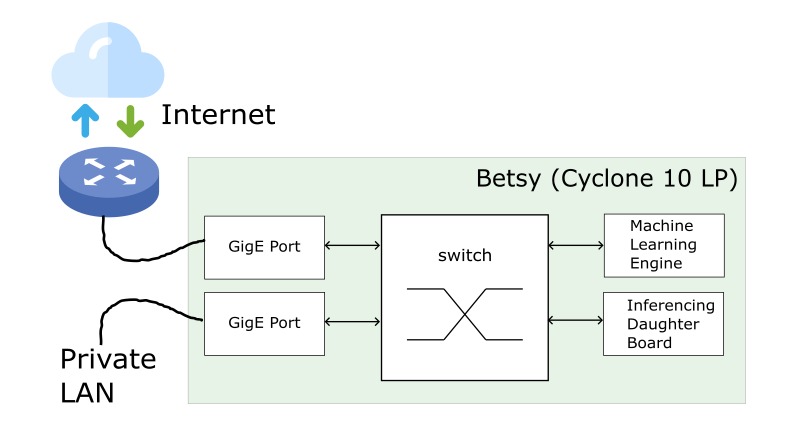

Figure 2 depicts a self-contained machine learning architecture utilizing the under development real-time inferencing daughter board. In this system scenario, the Cyclone 10 LP is directly transferring vectors / tensors encapsulated in an Ethernet frame to the Inferencing Daughter Board via its local high speed RGMII bus across the daughter board connectors.

Presentation Slides

The following slides were presented to the UNF IEEE group on 4/15/26.

The slide above mentions some of the design issues. Considering the tight schedule to design & manufacture the modules, the following updates to the slide are provided below.

- A PO has been submitted for the Agilex 3 A3CY050BB18AI6S (see more below).

- Interface between module and Betsy will use existing RGMII buses and the transfer of data will use Ethernet packets. In other words, the module will emulate a GigE Ethernet PHY.

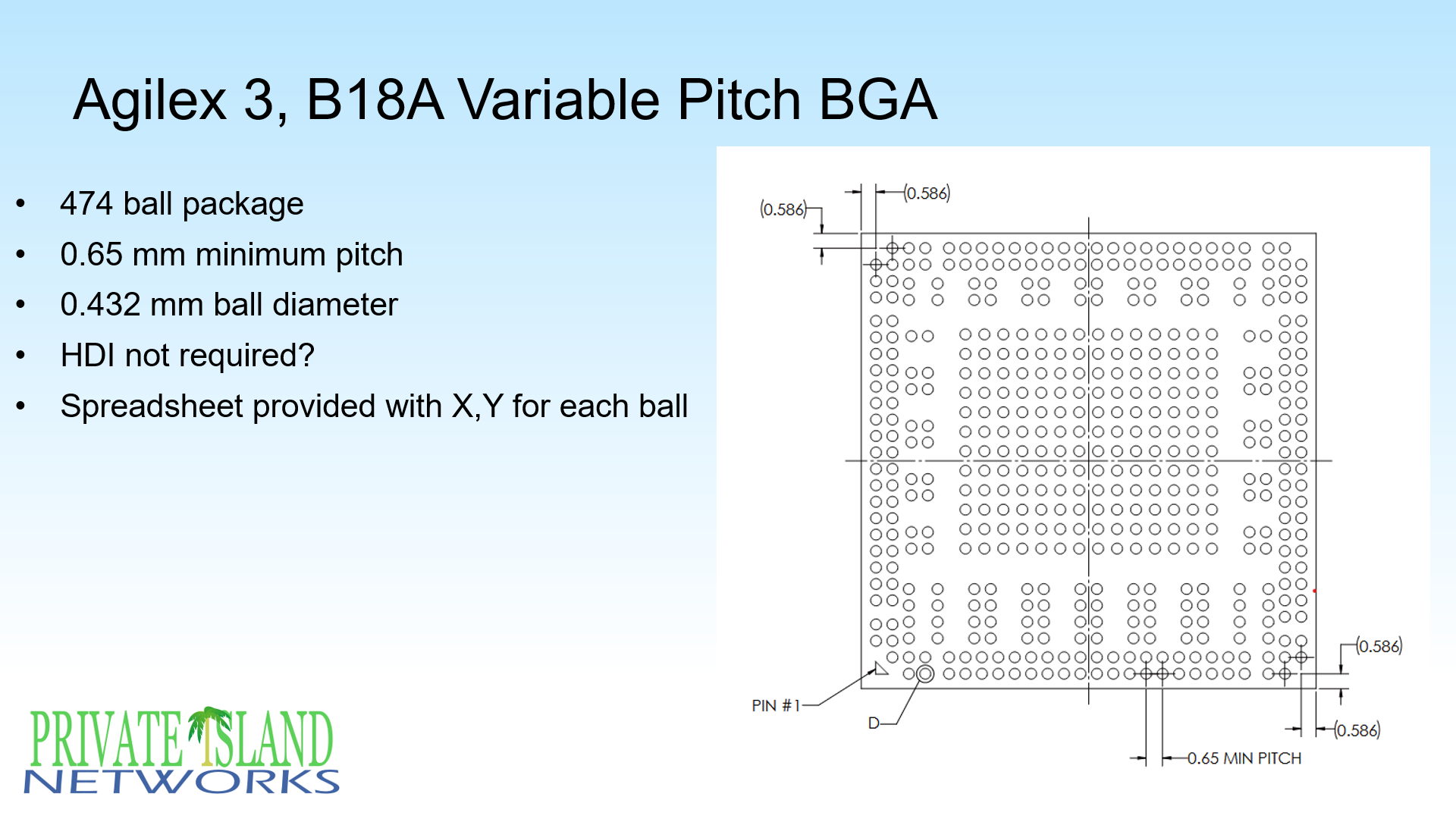

Regarding the ball locatons for the VPBGA, Altera provides a spreadsheet that defines the X,Y location of each package ball. The expectation is that the package does not require HDI PCB technology, such as VIP (VIA-in-PAD) and blind & buried VIAs. This requires validation.

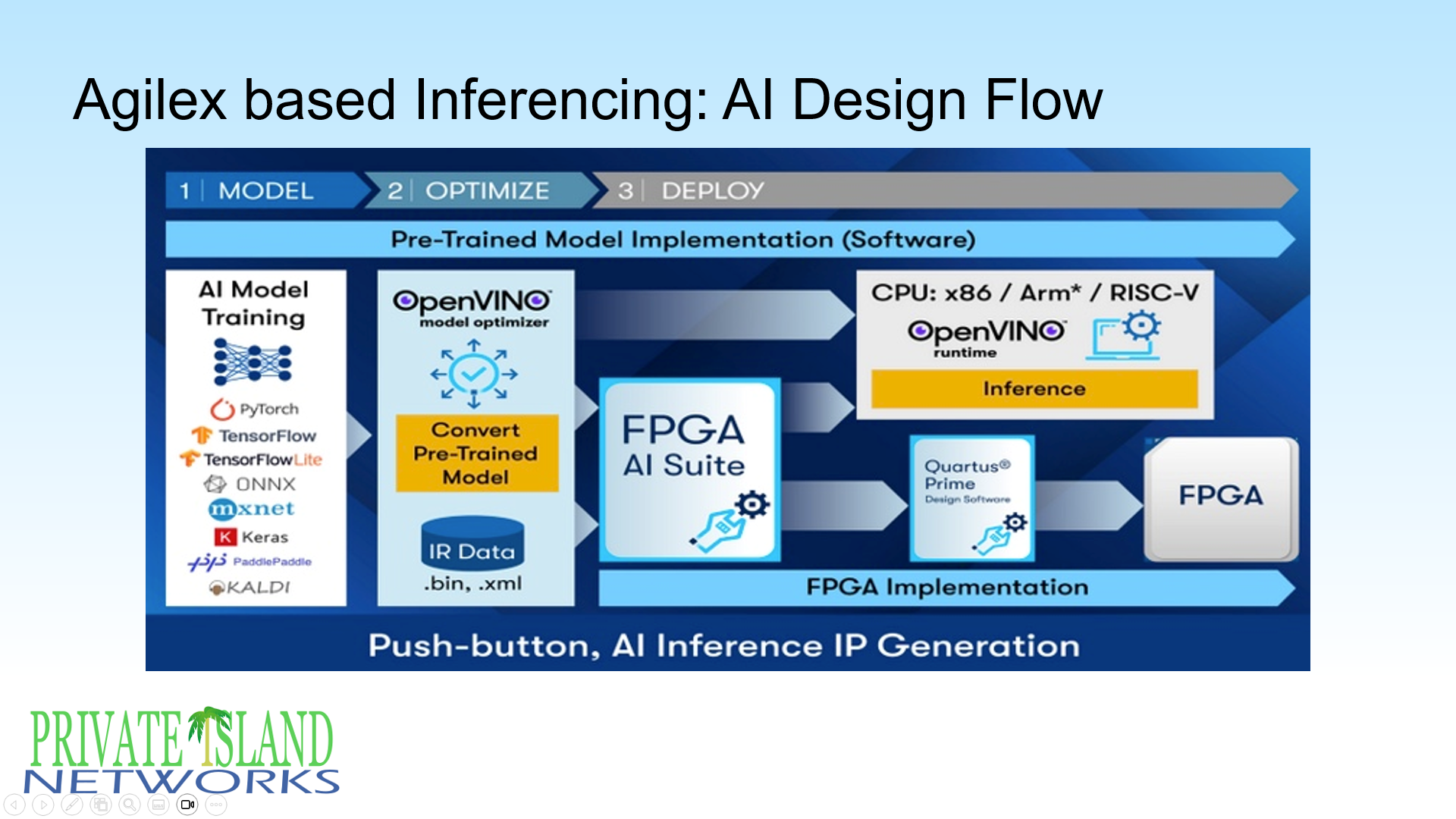

The slide above, which provides the Altera AI Design Flow, conveys the following information:

- The design flow supports all major AI frameworks for model creation, such as PyTorch and Keras.

- The OpenVINO framework converts the AI model to an Intermediate Represenation (IR Data).

- Using the FPGA AI Suite, the OpenVINO model can be targeted at a particular Altera FPGA. The model is integrated and compiled with the rest of the design using Quartus Prime Pro and ultimately instantiated on the FPGA device.

- Quartus Prime Pro is a free license for the Agilex 3. However, the AI Suite will apparently require a license, and work has started to have the required licenses available at UNF for this project.

Agilex 3 Device Overview

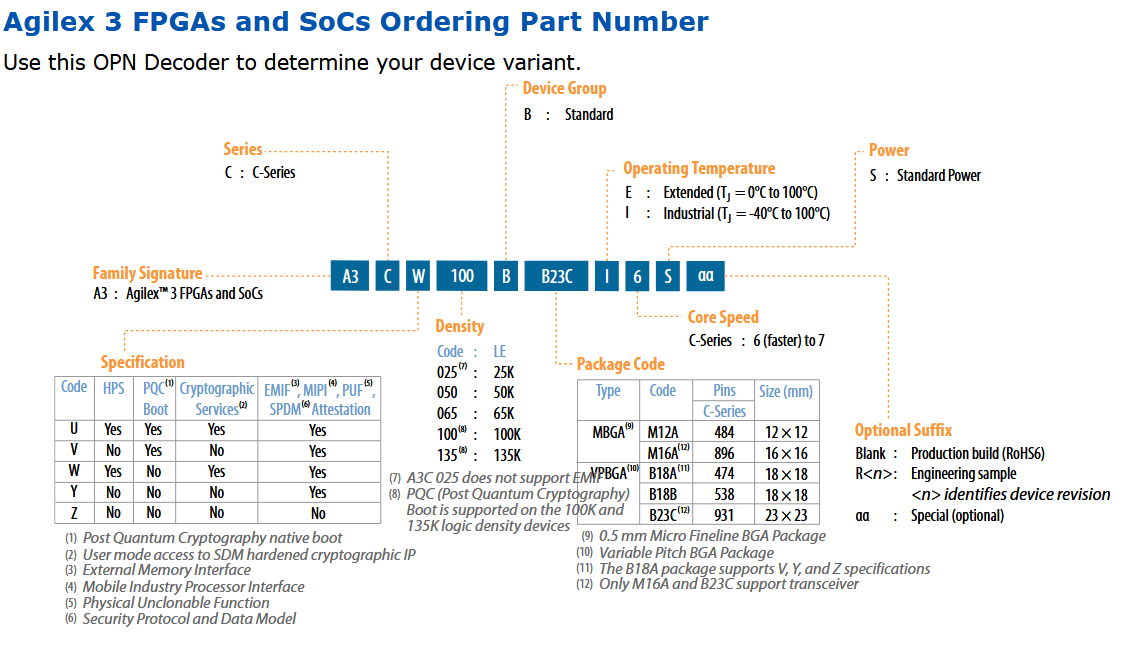

- A3CY050BB18AI6S (see decoder below)

- Specification Y (EMIF, but no HPA, Crypto, or PQC boot)

- 50K LE

- B18A 474 pin package (18mm x 18mm), VPBGA

- Industrial Temp (-40°C to 100°C)

- Speed Grade 6 (fastest)

Primary Work Threads

Listed below are the three work threads / areas required for this project:

- HW design, which includes determining the HW requirements, schematic capture & symbol library work, PCB layout and footprint library work, and transition to manufacturing. We will be using the open source KiCad for this project.

- FPGA Firmware (FW) design, which includes developing the Verilog source & project files, SystemVerilog test bench, simulation and verification, integration using Altera's Quartus Prime Pro, and some of the AI design flow

- AI / ML model development, which includes working with an ML framework, such as PyTorch, and integrating the model with the FPGA project using Altera's AI Design Flow, which also includes Intel's OpenVINO (see Figure 5 above). Extensive experimentation, testing, and tweaking will be necessary.

Design Resources

Altera Agilex 3 General

- Home Page for Agilex™ 3 FPGA and SoC FPGA

- Agilex™ 3 FPGAs and SoCs Device Overview

- Device Design Guidelines Agilex™ 3 FPGAs and SoCs

- General-Purpose I/O User Guide Agilex™ 3 FPGAs and SoCs

- Variable Precision DSP Blocks User Guide Agilex™ 3 FPGAs and SoCs

- Hyperflex Architecture High-Performance Design Handbook

Altera Agilex 3 Hardware Design

- KICAD Starting Project for ML Module.

- Agilex™ 3 FPGAs and SoCs Device Data Sheet

- Pin Connection Guidelines Agilex™ 3 FPGAs and SoCs

- Power Management User Guide Agilex™ 3 FPGAs and SoCs

- B18A (474) Package Ball Coordinates: Agilex™ 5 E-Series and Agilex™ 3 C-Series Devices

- PCB Design Guidelines Agilex™ 3 FPGAs and SoCs (See 9.3.2 for Voltage Regulator Selection)

- Agilex™ 3 FPGA and SoC C-Series Development Kit

FPGA Firmware (FW) Design

- Starting Quartus Project To Be Added soon.

- Quartus Prime Pro Edition Design Software Version 26.1

- Quartus® Prime Pro Edition User Guide Getting Started

- Settings File Reference Manual

- AN 903: Accelerating Timing Closure in Quartus Prime Pro Edition

- Questa*- Edition Simulation User Guide

FPGA AI/ML Design Flow

- Overview: FPGA AI Suite

- FPGA AI Suite Getting Started Guide

- FPGA AI Suite Handbook

- FPGA AI Suite Design Examples User Guide

- FPGA AI Suite Compiler Reference Manual

- FPGA AI Suite IP Reference Manual

Creating and Submitting Patches for Git Server

To Be Added.