This article summarizes the use & customization of the Private Island ® open source project and our 10G capable Volitio networking platform to implement an FPGA-based Ethernet video bridge & control system to meet the specific needs of our customer.

Our customer needed help with a proprietary, non-commercial camera system that utilizes 1G fiber transmission links and 8B/10B SERDES but does not implement Ethernet. Instead the 1G protocol over fiber is proprietary and specifically suited to the customer's application.

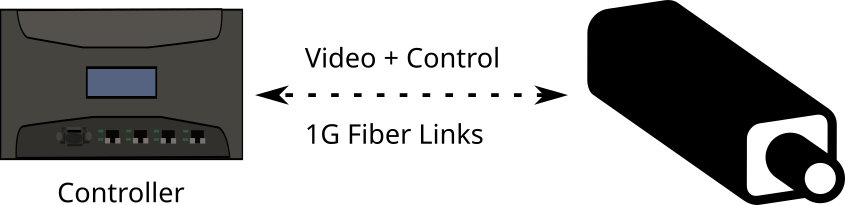

As shown in the figure below, the camera system consists of a controller chassis communicating via the aforementioned fibers to control the camera.

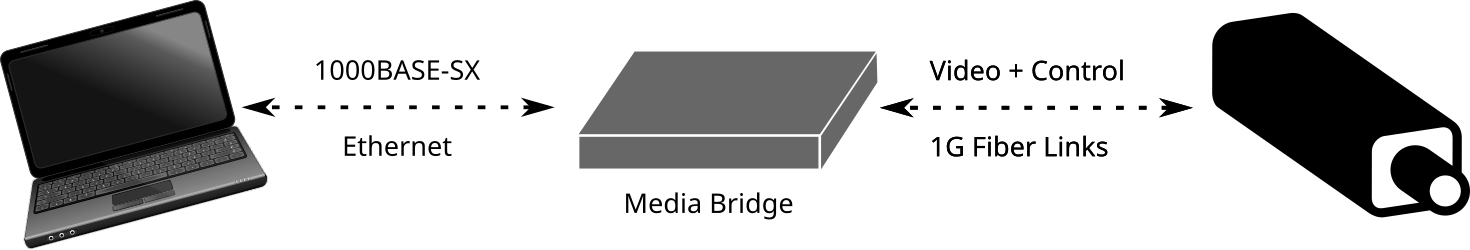

The requirement was to create a stand alone bridge between the proprietary system and standard Ethernet, so a PC could interface with the system over a standard LAN for the purposes of controlling the camera, receiving video, and debugging difficult to identify system issues.

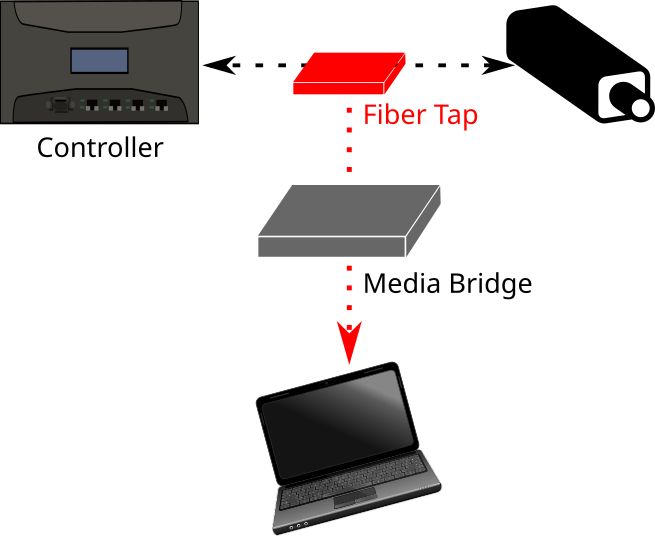

In one use case, the bridge connects directly to the camera to control and query it to determine its status and health. In another, the bridge receives real-time bidirectional communication between the camera and its control system using a passive fiber tap.

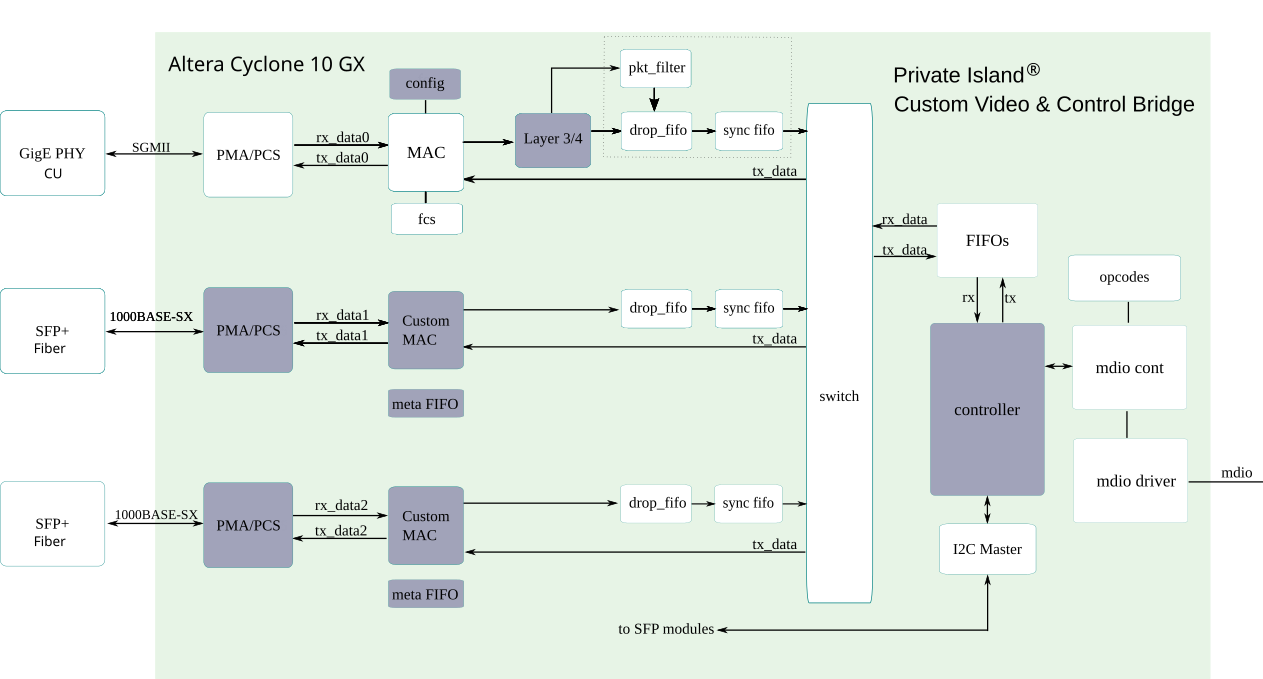

Shown below is a block diagram of the deployed FPGA architecture utilizing a customized version of the Private Island Verilog networking stack with the customized modules highlighted in grey. The FPGA on the Volitio board is an Altera Cyclone 10 GX with multiple 10G capable transceivers. The PMA/PCS blocks shown are Altera IP blocks and all other modules are written in behavioral Verilog.

Not shown in the figure are SMA connectors and a general purpose debug header on Volitio which were utilized heavily in the initial stages of development with an oscilloscope while the proprietary protocol was being analyzed.

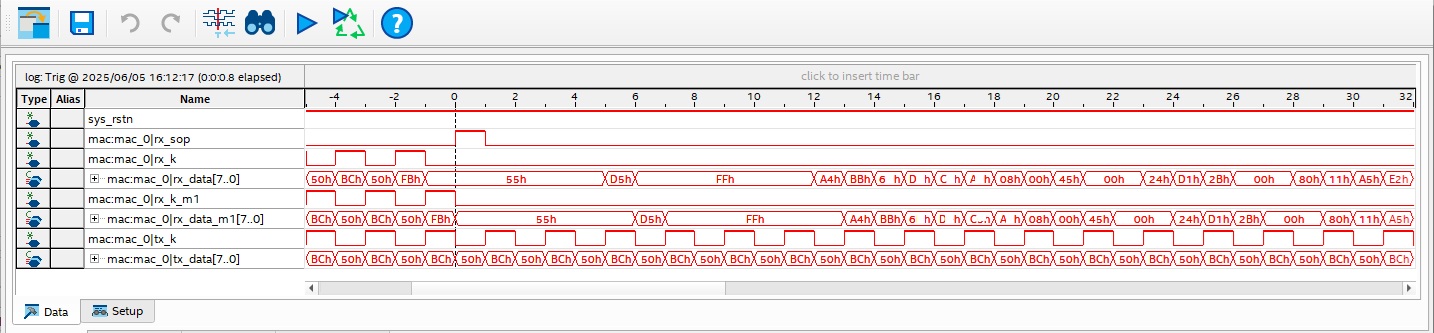

Some of the advantages in using the Altera Cyclone 10 GX are being able to use the world class Quartus Pro IDE and its Signal Tap embedded logic analyzer. The latter proved critical in fully understanding the customer's proprietary protocol. Signal Tap was used to capture the protocol over SERDES while varying its numerous control and video modes. This information was used in developing the requirements for the custom MAC module, Questa simulation test bench, and Python-based functional test utilities that were used to unit test the bridge before delivery to the customer.

Having full source for the custom Verilog MAC layer and fine grain control over the PCS/PMA IP were critical in developing a custom MAC layer to communicate directly with the system. For example, the PCS bit slip function was disabled that adjusts for clock differences between the embedded (remote) clock within the SERDES stream and the local low-jitter fabric clock. In place of the hard bit slip block, we customized a soft custom rate-matching logic block that dropped or inserted varying K codes that depended on the active mode across each fiber.

Having this degree of low-level control also enabled monitoring states such as loss of signal and running disparity, which were utilized by the customer's protocol and useful for system debugging.

For the customized soft internal controller, the customer's camera message protocol was implemented, so queries and modifications could be transmitted to the bridge via Ethernet. This enabled modifying various parameters in real-time and querying states, such as the FPGA's internal temperature and firmware version.

The initial systems have been delivered to the customer, and the feedback so far has been positive. Shown below is an early model of the bridge on the lab bench.